0 引言

模块化多电平换流器高压直流(modular multilevel converter based high voltage direct current,MMCHVDC)输电技术近十年来发展迅速。中国已陆续投运了上海南汇±18 kV柔性直流工程、南澳±160 kV三端柔性直流工程、舟山±200 kV五端柔性直流工程、厦门±320 kV柔性直流工程、云南±350 kV柔性直流工程、渝鄂±420 kV背靠背柔性直流工程,正在建设的有张北±500 kV柔性直流电网工程以及乌东德±800 kV混合多端直流输电工程[1]。柔性直流输电技术在中高压等级电能输送领域有广阔的应用前景[2-3]。

随着电压等级的不断提高,在现有硬件水平下阀控链路延时的重要性逐步突显出来。文献[4-7]研究了控制延时对系统动态性能的影响,分析表明控制延时越大,系统稳定性越差,甚至无法稳定工作,同时也提出了优化延时、改善系统性能的策略。文献[8]首次研究了柔性直流输电系统的链路延时对系统动态性能的影响,阐述了高压柔性直流输电系统因控制保护装置多、不同控制保护装置间通信数据多等原因,控制链路延时远大于一个控制周期。控制链路延时的大幅增加恶化了系统的动态响应特性,降低了交流故障穿越能力。文献[8]同时提出了通过一种不影响幅频特性的相位校准方法进行系统补偿,提高系统稳定性。

综上所述,控制链路延时的增加会恶化系统运行特性,在系统扰动情况下容易引发功率振荡,同一工程中不同厂家装置延时的不一致将导致振荡特性更加复杂。限制阀控系统控制链路延时成为优化站控系统、保证系统稳定的必要前提,应制定控制装置出厂实验的强制性校验标准,制定统一的阀控延时标准。本文在研究柔性直流输电系统中阀控装置内部延时组成的基础上,提出下行、上行、过流保护3项延时测试方法,并以昆柳龙柔直输电工程柳州极1换流站阀控为例,开展测试并详细分析测试结果,最后提出了进一步优化方向。

1 阀控链路延时分析

1.1 阀控硬件架构

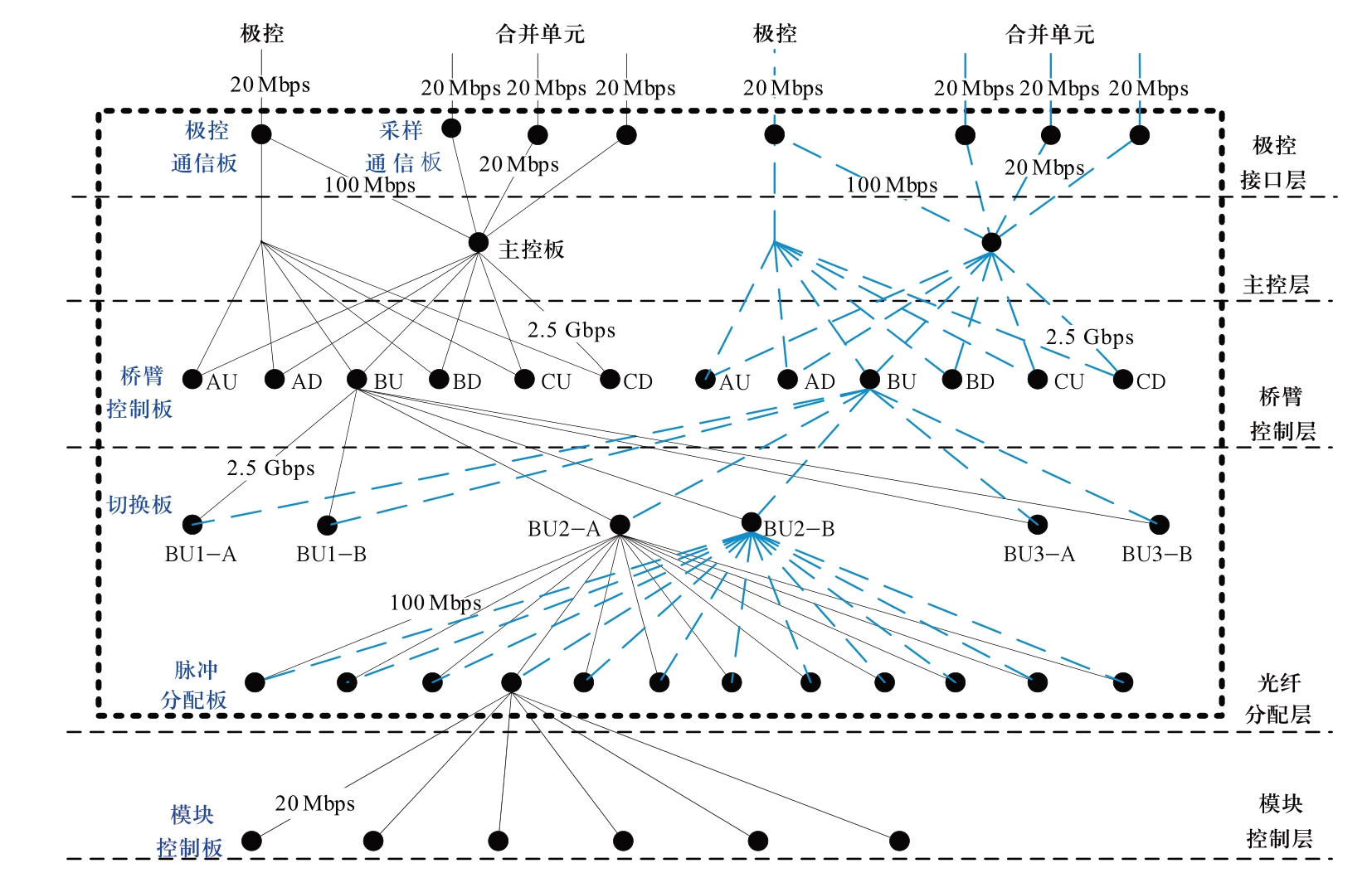

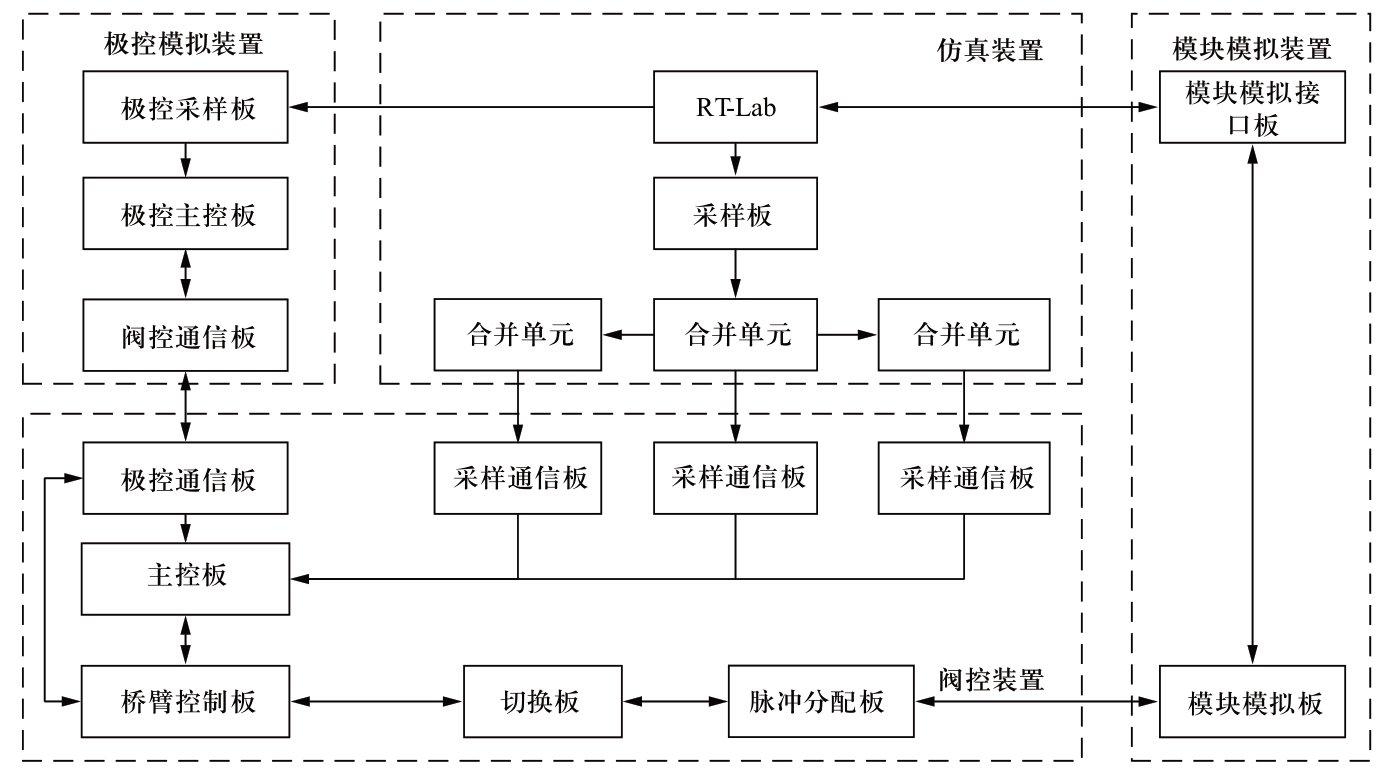

阀控硬件分为极控接口层、主控层、桥臂控制层、光纤分配层、模块控制层5部分。由于阀控脉冲分配屏及模块数量较多,图1仅以B相上桥臂中的1个脉冲分配机箱及机箱中的1个脉冲分配板进行示意。备用套主控机箱连线为图中蓝色虚线所示,黑色虚线框内为阀控内部通信。

阀控装置中主控机箱分为互为冗余的A套与B套,每套阀控装置独立地与极控交互数据。极控接口层分为控制数据交互链路和采样数据交互链路。极控控制数据一方面通过极控通信板接收数据后转发至阀控主控板,由主控板进行顺控、环流抑制等控制及算法处理;另一方面直接转发至阀控桥臂控制板,由阀控桥臂控制板接收极控数据,完成均压并产生触发脉冲。阀控状态数据一方面通过桥臂控制板发送至极控通信板,另一方面通过主控板发送至极控通信板,最终在极控通信板汇总阀控状态数据发送至极控。合并单元采样数据分3路进入每个阀控主控机箱,3路数据在采样通信板卡中完成数据接收、数据处理和数据保护定值比较。处理后的保护信号通过快速保护专用通道传送至主控板,由主控板完成三取二判断逻辑。最终判断结果通过快速保护信号线传送至桥臂控制板,由桥臂控制板出口保护数据至脉冲分配机箱。

阀控装置的脉冲分配机箱内A、B两块切换板卡互为冗余,分别与2套主控机箱的桥臂控制板进行数据交互,根据主备状态选择有效数据下发,形成交叉冗余通信。脉冲分配板可与A、B两块切换板进行通信,根据主备状态选择有效数据下发至模块。

图1 阀控链路延时相关硬件拓扑

Fig.1 Hardware topology for communication link delay of valve control system

1.2 阀控下行链路延时分析

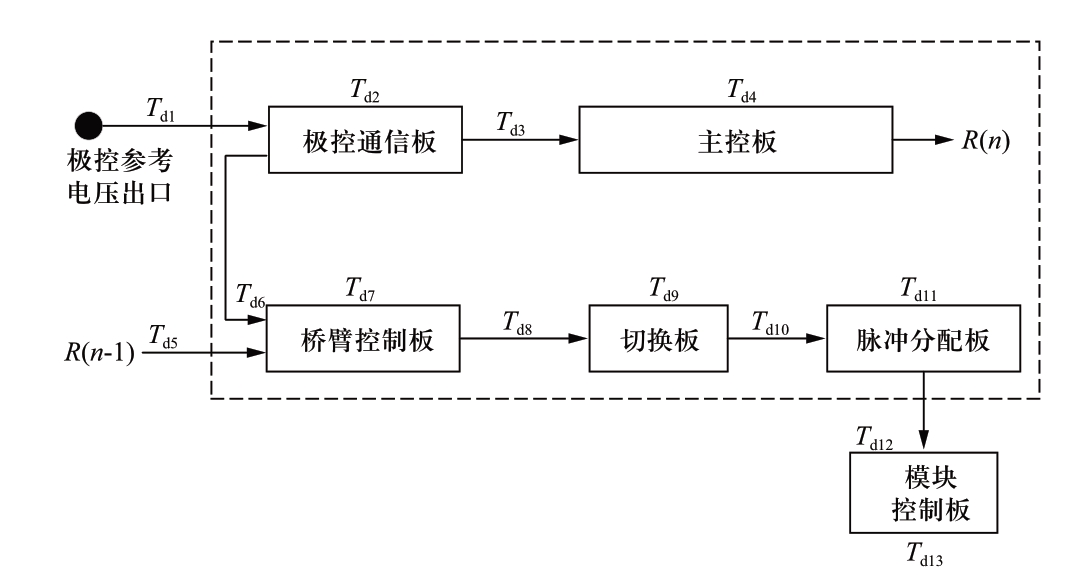

本文定义阀控下行链路延时为阀控接收到调制波至模块控制板按照该调制波输出功率开关器件驱动指令的时间。实际工程中功率开关器件还有对应的死区保护时间和开通/关断时间。图2为阀控下行链路延时说明示意图。

图2 阀控下行链路延时说明示意图

Fig.2 Description of valve control downlink delay

图2中Td1为极控至阀控通信数据传输延时,不在阀控链路延时之内。R(n)为经过主控板计算的控制数据结果,该部分延时由Td2+Td3+Td4+Td5组成。主控板计算后发送至桥臂控制板,因该数据对下行控制仅对环流抑制起一部分补偿作用,可以使用上一周期的计算结果R(n-1),桥臂控制板无需等待本周期的补偿数据,因此该部分延时不计在阀控链路延时之内。

由于桥臂控制板直接接收极控通信板转发极控的控制数据,接收后根据该控制数据产生点火脉冲,子模块电压排序过程不需要等待极控控制数据,可以提前完成排序,使得排序不再占用下行链路延时。桥臂控制板接收到极控数据后进行降损处理并产生点火脉冲,该过程延时为Td6+Td7。

桥臂控制板完成点火脉冲后将其传送至切换板,通信速率为2.5 Gbps,通信延时为Td8。

切换板接收到桥臂控制板控制数据后进行主备状态选择及数据稳定性判断,该延时为Td9。完成判断后即可发送至脉冲分配板,通信速率为100 Mbps,通信延时为Td10。

脉冲分配板接收到切换板控制数据后进行主备选择及数据稳定性判断,该延时为Td11。脉冲机箱与模块控制板之间通信周期为Td12,通信速率为20 Mbps,故最大延时为Td12。

实际功率器件动作分为开通与关断2种,关断时间不受死区影响,开通时间需要延时1个死区时间,死区时间为Td13。本文主要关注阀控系统的延时,功率器件的延时不计算在阀控下行链路延时中。

综上所述,根据阀控下行链路延时定义,阀控理论下行链路总延时Tdtotal计算公式如下:

1.3 阀控过流保护链路延时分析

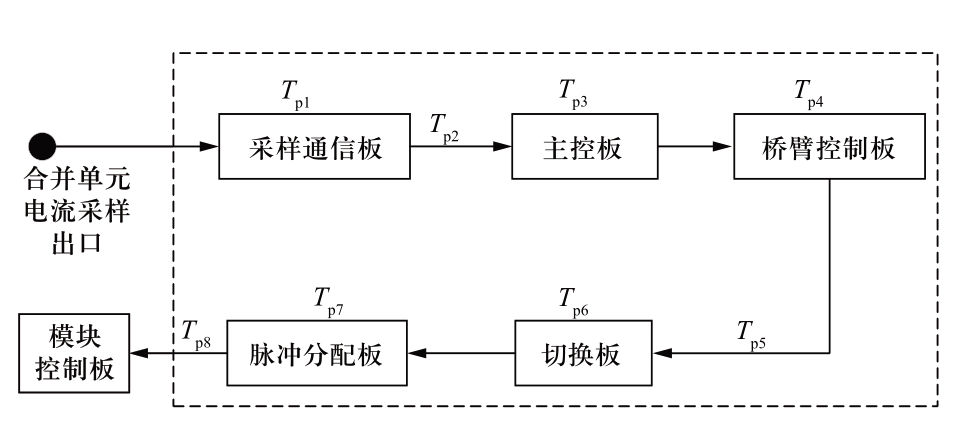

本文定义过流保护链路延时为阀控接收到第一个故障点数据至子模块闭锁的时间。图3为阀控过流保护链路延时说明示意图。

图3 阀控保护链路延时说明示意图

Fig.3 Description of valve control protection delay

图3中Tp1为采样通信板判断过流的时间,目前一段、二段和di/dt过流保护均需连续确认3个点为过流才会报出,采样频率为100 kHz,故判断时间为20 μs。采样通信板判断过流后通过专用通道传送至主控板,该通信发送周期为Tp2,故通信最大延时为Tp2。

主控板接收到过流信号后进行三取二判断,数据处理时间为Tp3。判断过流故障后通过快速保护信号线发送至桥臂控制板。

桥臂控制板对保护信号进行滤波确认,滤波延时为Tp4。由于桥臂控制板与切换板之间通信周期为25 μs,若过流时刻出现在刚发完一帧数据后,则需要等待 25 μs才可将保护信号下发至切换板。为避免此类情况,在桥臂控制板需要下发快速保护信号时插入一帧数据,及时将保护数据下发。目前插入保护数据周期为12.5 μs,根据需要可将此时间进一步缩短至6.25 μs或更短,故Tp5当前最大值为12.5 μs。

切换板接收到保护数据后进行主备状态判断,经过数据确认后通过快速保护信号线发送至脉冲分配板,判断及确认延时为Tp6。保护信号经过脉冲分配板确认后下发至子模块,滤波延时为Tp7。

脉冲机箱与模块控制板之间采用20 Mbps通信波特率,通信周期为5 μs,故Tp8最大延时为5 μs。

综上所述,理论上阀控过流保护链路最大延时为Tptotal:

由于存在Tp2和Tp5,故最大延时与最小延时存在由于通信周期带来的偏差,偏差值为Tp2和Tp5之和,TpΔ定义如下:

1.4 阀控上行链路延时分析

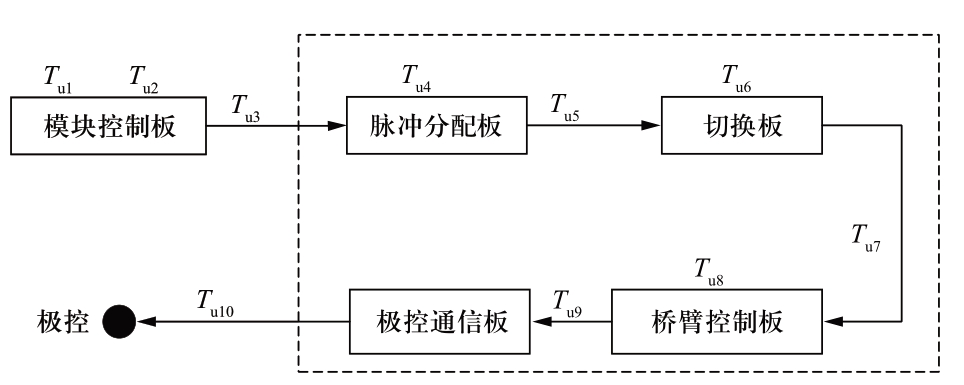

定义模块电容电压上行链路延时为电容电压硬件采样前端信号至阀控计算得到子模块全局平均电压出口的延时。图4为阀控上行链路延时说明示意图。

图4 阀控上行链路延时说明示意图

Fig.4 Description of valve control uplink delay

图4中子模块电容电压采样硬件采样带宽设计为100 kHz,其延时估算约Tu1。模数转换周期为5 μs一个采样点,软件完成4个点的滑动滤波,其延时估算为Tu2。子模块与脉冲分配板之间通信周期为Tu3。故子模块采样和通信传输时间为Tu1+Tu2+Tu3。

图5 阀控全链路试验平台

Fig.5 Generic experimental setup of valve control test

阀控脉冲分配板接收到模块数据后进行数据处理,数据处理耗时Tu4。脉冲分配板完成数据处理后将数据发送至切换板,通信波特率为100 Mbps,传输通信延时为Tu5。故脉冲分配板处理上行数据总延时为Tu4+Tu5。

切换板接收到脉冲分配板数据后进行数据处理,耗时Tu6,处理后发送数据至桥臂控制板,通信波特率为2.5 Gbps,数据传输通信延时为Tu7。切换板处理上行数据总延时为Tu6+Tu7。

桥臂控制板接收到切换板数据后进行数据处理,耗时为Tu8。由于硬件限制,各相桥臂控制板通过分时复用同一通信通道的方式将数据发送至极控通信板,通信波特率为20 Mbps,传输通信总耗时为Tu9。此处分时通信耗时较多,后续可做进一步优化。故桥臂控制板处理上行数据总延时为Tu8+Tu9。

极控通信板接收上行数据后发送至极控,通信波特率为20 Mbps,传输通信延时为Tu10,该传输延时不算在阀控上行链路延时之中。

综上所述,阀控理论上行链路总延时为Tutotal:

2 阀控链路延时测试方案

阀控全链路测试试验硬件由仿真装置、模块模拟装置、极控模拟装置和阀控装置组成,图5仅对主要链路连接关系进行说明。仿真装置包含RT-Lab仿真机箱和合并单元模拟部分,由仿真装置提供阀硬件模拟及测试环境搭建。极控模拟装置接收仿真装置及阀控的状态数据,经过控制运算后传送控制数据至阀控。模块模拟装置可提供模块控制板的功能,模拟全链路所有模块与阀控装置互联。

阀控链路延时测试应保证阀控内部通信完整性,一般采用物理分光器的方式进行测试。以下分别介绍3种延时的测试方案。

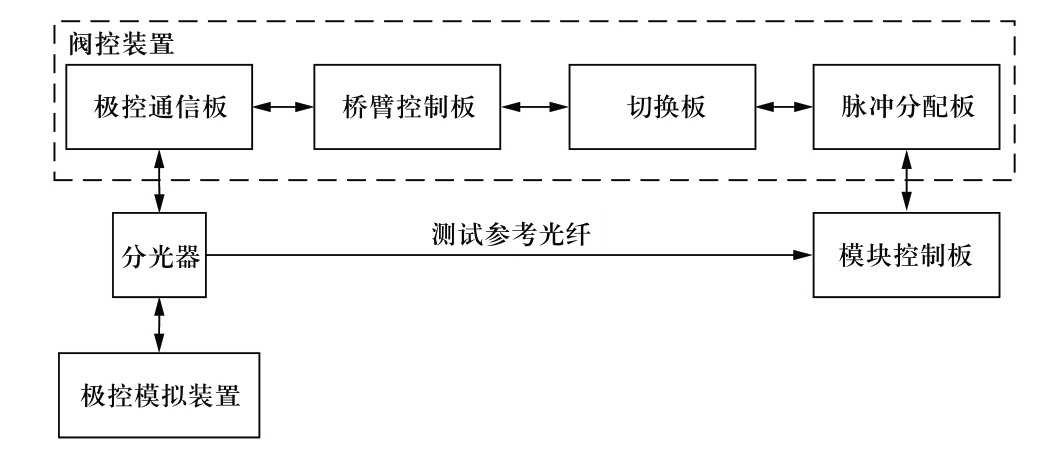

2.1 阀控下行链路延时测试方法

如图6所示,在极控模拟装置至阀控下行通信光纤间增加物理分光器,将极控模拟装置下行光纤链路分成2路,一路连接阀控装置,另一路连接外置模块控制板。

外置模块控制板需要具备2对通信光纤接入能力,一路连接阀控脉冲分配板,另一路连接来自分光器的参考测试光纤。

图6 阀控下行链路延时测试方法

Fig.6 Delay time measurement of valve control downlink

被测链路为极控模拟装置、极控通信板、桥臂控制板、切换板、脉冲分配板、模块控制板的传输链路。参考链路为极控至模块控制板的传输链路。

测试需要全部模块在投入和全部全桥模块负投入2种状态间反复切换,以观测某一个全桥模块的功率开关器件导通关断与调制波变化的延时情况。故需要极控模拟装置设定调制波来实现该功能。该调制波电压Vset可通过下式计算。

式中:Nm为单桥臂模块数量;Vn为单个模块额定电压;k为调制波比例系数。在昆柳龙直流工程中,k为0.05,Vn为2100 V,Nm为216。

可得出极控输出调制波电压标幺值需要在±22 680之间切换。切换周期需远大于链路延时时间,根据估算,阀控链路延时小于100 μs,故切换周期可设置为 1 ms。

测试时需将阀控保持解锁状态。测试时可使用模块控制板CPLD中增加软件示波器,观测参考调制波变化和模块产生的功率器件驱动信号变化之间的延时,该延时即为阀控下行链路延时。

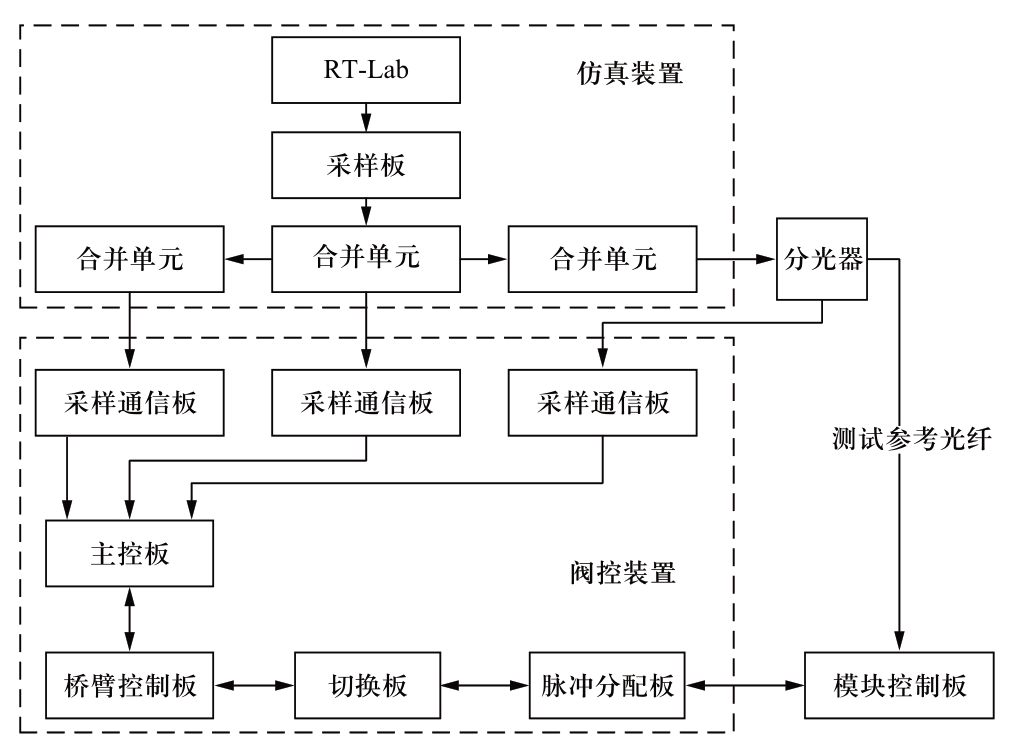

2.2 阀控过流保护链路延时测试方法

如图7所示,在合并单元某一条光纤增加物理分光器,分光后一路正常连接阀控,另一路作为测试参考链路连接模块控制板。

被测链路为合并单元、采样通信板、主控板、桥臂控制板、切换板、脉冲分配板、模块控制板。参考链路为合并单元至模块控制板的传输链路。

图7 阀控过流保护链路延时测试方法

Fig.7 Delay time measurement of valve control overcurrent protection

为精确、可靠测试过流保护链路延时,需要模拟阶跃电流信号。模拟过流可以通过采样板FPGA产生,电流数据需要在未过流和过流之间进行切换,过流数据需保持3个采样点以上,切换周期需要大于10倍估算过流保护延时。模拟di/dt过流需要根据采样周期进行过流数据累加,每次累加大于di/dt阈值,持续3个周期即可。

由于估算阀控过流保护链路延时小于100 μs,故切换周期需大于1 ms。由于阀控一个采样点时间为10 μs,故过流保持时间需要大于20 μs。

测试时需将阀控保持解锁状态,只有过流故障出现后进行暂时性闭锁,过流故障恢复后阀控仍然恢复解锁状态。

在测试过程中使用模块控制板CPLD增加软件示波器,观测参考电流数据变化和模块产生的功率器件驱动信号变化之间的延时,该延时即为阀控过流保护链路延时。

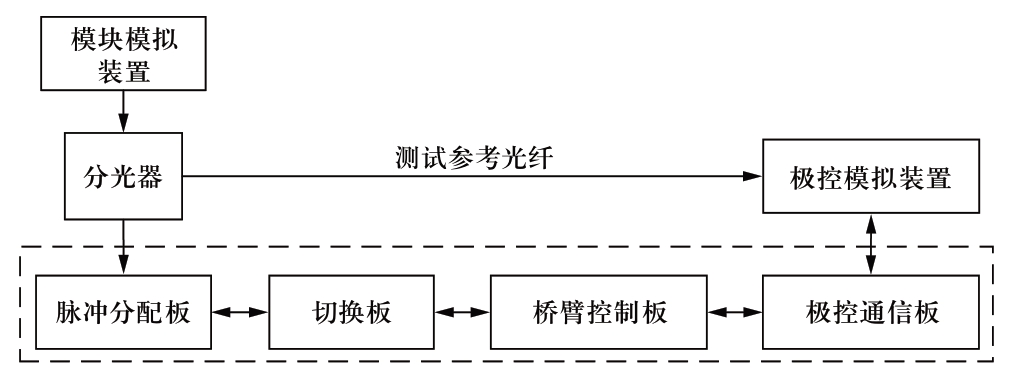

2.3 阀控上行链路延时测试方法

如图8所示,在模块模拟装置其中一路上行光纤增加物理分光器,分光后一路正常连接至阀控装置,另一路作为测试参考链路连接至极控模拟装置中的阀控通信板。

被测链路为模块模拟设备、脉冲分配板、切换板、桥臂控制板、极控通信板、极控模拟装置的传输链路。参考链路为模块模拟装置至极控模拟装置的传输链路。

图8 阀控上行链路延时测试方法

Fig.8 Delay time measurement of valve control uplink

测试过程中通过模块模拟装置产生桥臂电压同时产生阶跃,通过对比极控模拟装置中阀控通信板接收的全局平均电压与测试参考数据变化之间的延时即可得出阀控上行链路延时。实际1个桥臂的模块是由 2个模块模拟机箱组成,由于仿真系统中RT-Lab仿真设备至2个模块模拟机箱的同步性无法保证,无法在同一时刻产生某一桥臂模块的电压阶跃。故测试方法更改为通过模块模拟机箱后台控制一个机箱中108个模块电压同时刻阶跃变化的方式。

通过模块模拟后台下发定电圧命令至AU的第1至第108模块,电压设定在800 V和2200 V反复交替,其余模块电压由RT-Lab设置为554 V。观测极控中阀控通信板接收分光器数据和接收阀控全局模块平均电压数据之间的延时。

在模块模拟装置后台设定部分模块电压,理论全局模块电压为:

式中:Vavg为全局子模块平均电压;Vset为通过模块模拟装置后台设置的模块电压;Nset为通过模块模拟装置后台设置的模块数量;Vn为RT-Lab默认设置的模块电压;Nn为6个桥臂总模块数。

将AU桥臂中108个模块电压设定为800 V,其余1188个模块电压设定为554 V,全局模块平均电压应为574 V;将AU桥臂中108个模块设定为2200 V,其余1188个模块设置为554 V,全局模块平均电压应为691 V。

由于阀控装置与极控模拟装置之间定义模块全局平均电压值的2100 V对应标幺值1000,故阀控装置传送至极控模拟装置的数据需要标幺化处理,如式(7)所示。

式中:Vp为全局子模块平均电压标幺值;Vavg为全局子模块平均电压值;kp为标幺系数。

设置AU桥臂中108个模块电压为800 V时极控接收模块全局平均电压标幺值为273;设置AU桥臂中108个模块电压为2200 V时极控模拟装置接收模块全局平均电压标幺值为329。

测试过程中极控模拟装置接收到全局模块平均电压标幺值应该在273和329之间变化。

3 阀控链路延时测试实验及结果

被测阀控装置、极控模拟装置、合并单元模拟装置和RT-Lab如图9所示,应尽可能降低RT-Lab与极控模拟装置间连接线路长度,避免因为模拟信号线损导致系统控制问题。阀控装置由2个主控屏柜和6个脉冲屏柜组成。极控模拟装置由1个屏柜构成。极控模拟装置与阀控装置间的接口与昆柳龙直流项目保持一致。合并单元由一个机箱组成,通过采样RT-Lab输出的模拟信号,将采样数字信号按照合并单元的协议发送至阀控装置。

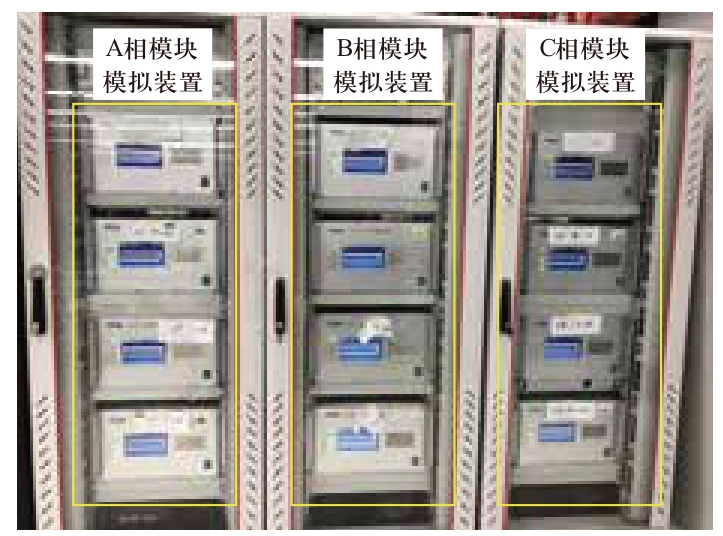

模块模拟装置如图10所示,该设备由3个屏柜组成,每个屏柜包含4个仿真机箱,每个机箱可模拟108个模块,每个屏柜具备2个桥臂的模块模拟功能。该模块模拟装置实现的功能与工程子模块功能相近。

图9 被测阀控设备与RT-Lab仿真设备

Fig.9 Experimental setup of valve control equipment and RT-Lab

图10 模块模拟装置

Fig.10 Experimental setup of module simulation equipment

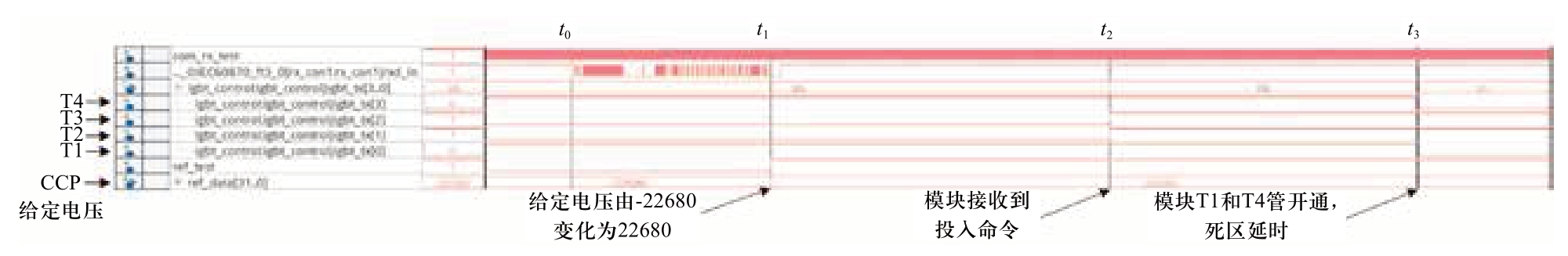

3.1 阀控下行链路延时测试结果

按照前文所述测试方式进行20组数据测试,观察延时有无波动,选取最大延时作为阀控下行链路延时。

如图11所示,采样时钟为100 MHz,定义模块正投入驱动波形有效时刻为t3,模块控制板接收到正投入命令时刻为t2,参考测试通道接收到正投入数据时刻为t1,参考测试通道数据帧发送起始时刻为t0。可以得出极控模拟装置至阀控装置通信传输时间Td1为:

阀控装置接收到极控模拟装置全部正投入命令至模块控制板接收到投入命令之间的时间为Tdtotal:

子模块默认死区时间参数为Td13。

图11中igbt_tx[3:0]为IGBT驱动信号,“0”表示导通功率开关器件;“1”表示关闭功率开关器件。ref_data为极控模拟装置发出的调制波数据,“-22680”表示所有全桥全部负导通;“22680”表示全部子模块正导通。

图11 阀控下行链路延时测试结果(最大延时)

Fig.11 Test results of valve control downlink delay(max)

3.2 阀控过流保护链路延时测试结果

按照前文所述测试方式进行20组测试,观察延时有无波动,选取最大延时作为阀控过流保护链路延时。

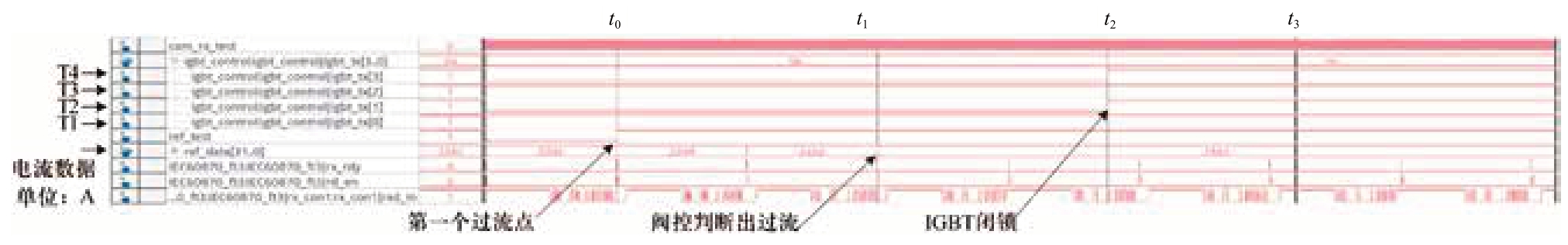

di/dt过流测试最大延时测试波形如图12所示,IGBT闭锁时刻为t3处,阀控判断出di/dt过流时刻为t1处,检测判断时间为20 μs,可以得出di/dt过流至IGBT闭锁总时间为Tpmax。

如图13所示,di/dt过流测试过程中最小延时为Tpmin,超前最大延时为TpΔ。实测结果小于前文分析的理论最大最小延时差值。

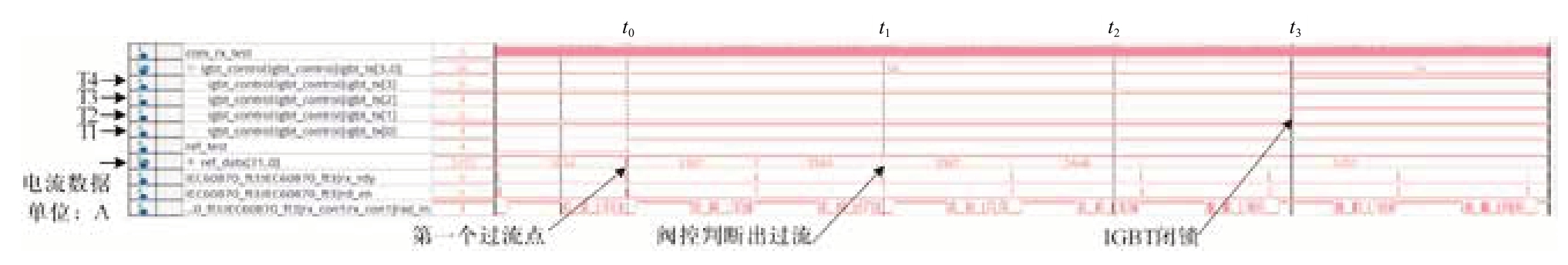

一段过流测试20组数据,其最大延时与di/dt测试结果一致,如图14所示。此处不再赘述一段过流的延时测试,可以参考di/dt的测试数据。

图12至图14中igbt_tx[3:0]含义与图11相同。ref_data为接收到电流采样数据。ref_test信号为过流标志位,“1”表示检测到过流,“0”表示未检测到过流。

图12 di/dt过流延时测试结果(最大延时)

Fig.12 Test results of di/dt overcurrent delay(max)

图13 di/dt过流延时测试结果(最小延时)

Fig.13 Test results of di/dt overcurrent delay(min)

图14 一段过流延时测试结果(最大延时)

Fig.14 Test results of first level overcurrent delay(max)

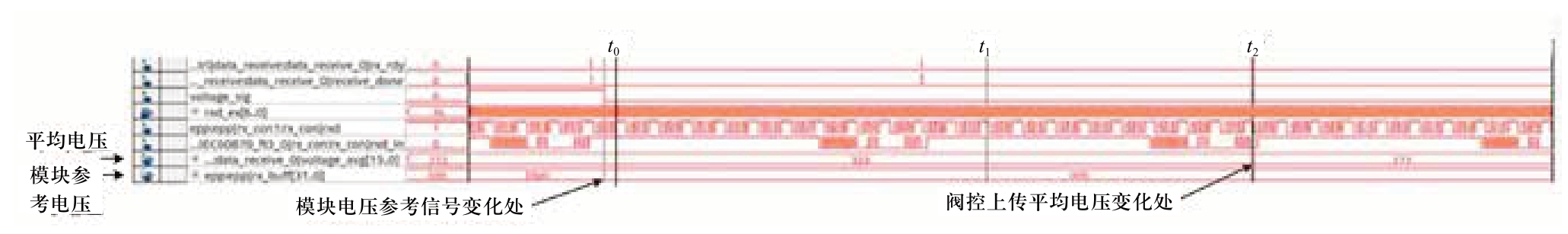

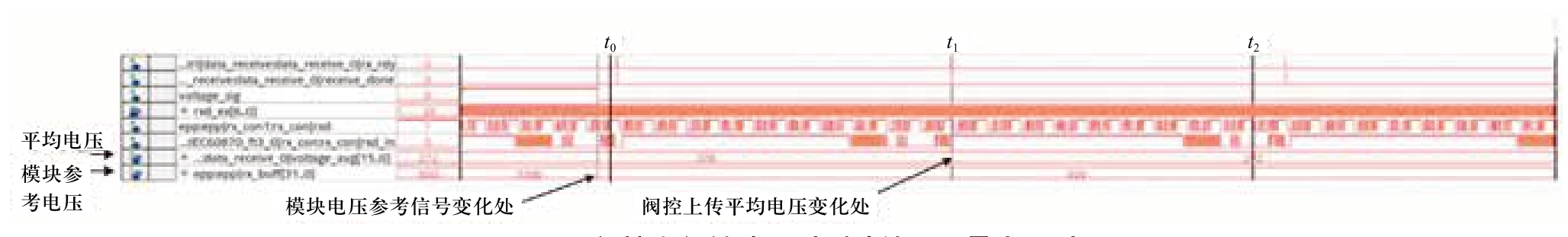

3.3 阀控上行链路延时测试结果

按照前文所述测试方式进行20组测试,观察延时有无波动,选取最大延时作为阀控上行链路延时。

上行链路最大延时测试结果如图15所示,定义参考测试通道接收到电压由2200 V变为800 V的时刻为t0,实际极控模拟装置接收到的平均电压标幺值由328(FPGA计算数据取整误差导致与理论计算有差异)变为272的时刻为t2,故上行最大延时测试结果为Tumax。

上行链路最小延时测试结果如图16所示,定义参考测试通道接收到电压由2200 V变为800 V的时刻为t0,实际极控模拟装置接收到平均电压的标幺值由328变为272的时刻为t1。故上行最小延时测试结果为Tumin。

图15和图16中,rxd信号为参考测试链路解码后的通信数据。rxd_in为接收阀控链路解码后的通信数据。voltage_avg为接收阀控上传的全局子模块平均电压标幺值。rx_buff为接收参考测试链路单模块电压采样值。为了方便观察,voltage_sig为参考测试链路单个子模块电压变化标志,“1”表示接收到的电压为 2200 V,“0”表示接收到的电压为800 V。

如前文中对阀控上行链路延时的定义,上行链路延时包含子模块至阀控通信延时和子模块硬件软件滤波时间,但不包含阀控装置至极控模拟装置的通信延时。由于产生电压阶跃时刻与阀控装置和极控模拟装置通信周期不同步,故实测最大最小上行延时会相差一个阀控装置与极控模拟装置通信的通信周期。最大上行延时测试结果应加上修正系数。

图15 阀控上行链路延时测试结果(最大延时)

Fig.15 Test results of valve control uplink delay(max)

图16 阀控上行链路延时测试结果(最小延时)

Fig.16 Test results of valve control uplink delay(min)

式中:TuΔ为上行链路延时修正系数;Tu3为模块至阀控通信延时;Tu1为子模块硬件滤波时间;Tu2为子模块软件滤波时间;Tu10为阀控至极控的通信延时;Tcyc为阀控装置至极控模拟装置的通信周期。

但由于实测取样样本有限,测试结果最大最小上行链路延时相差TΔ与Tcyc有一定偏差。

综上所述,阀控上行链路延时实测修正后为Tutotal:

4 结论

本文结合昆柳龙直流输电工程柳北换流站极1换流阀阀控的应用情况,分析了阀控各部分延时的组成,定义了阀控下行链路延时、阀控过流保护链路延时和阀控上行链路延时的范围,提出了阀控延时测试方法,依据链路延时定义和测试方法进行了测试。

测试结果与理论计算一致,符合设计预期。通过阀控链路延时的测试与分析,得出以下优化方向:阀控下行链路延时中桥臂控制板均压及点火脉冲生成部分占用时间较长,可进一步优化;阀控过流保护延时中桥臂控制板插入保护数据帧周期可进一步缩短;阀控上行链路延时理论中桥臂控制板至极控通信板的分时传输方式占用时间较长,仍有优化空间。

参考文献

[1]汤广福,庞辉,贺之渊.先进交直流输电技术在中国的发展与应用[J].中国电机工程学报,2016,36(7):1760-1771.

TANG Guangfu, PANG Hui, HE Zhiyuan.R & D and application of advanced power transmission technology in China[J].Proceedings of the CSEE, 2016, 36(7):1760-1771(in Chinese).

[2]吴方劼,马玉龙,梅念,等.舟山多端柔性直流输电工程主接线方案设计[J].电网技术,2014,38(10):2651-2657.

WU Fangjie, MA Yulong, MEI Nian, et al.Design of main connection scheme for Zhoushan flexible multi-terminal HVDC transmission project[J].Power System Technology, 2014, 38(10):2651-2657(in Chinese).

[3]李岩,罗雨,许树楷,等.柔性直流输电技术:应用、进步与期望[J].南方电网技术,2015,9(1):7-13.

LI Yan, LUO Yu, XU Shukai, et al.VSC-HVDC transmission technology:application, advancement and expectation[J].Southern Power System Technology, 2015, 9(1):7-13(in Chinese).

[4]ZOU C Y, LIU B Y, DUAN S X, et al.Influence of delay on system stability and delay optimization of grid-connected inverters with LCL filter[J].IEEE Transactions on Industrial Informatics, 2014, 10(3):1775-1784.

[5]WANG J G, YAN J D, JIANG L, et al.Delay-dependent stability of single-loop controlled grid-connected inverters with LCL filters[J].IEEE Transactions on Power Electronics, 2016, 31(1):743-757.

[6]邹常跃,刘邦银,段善旭,等.并网逆变器中数字控制延时对系统稳定性的影响及其优化设计[J].中国电机工程学报,2015,35(2):411-417.

ZOU Changyue, LIU Bangyin, DUAN Shanxu, et al.Influence of delay on system stability and its optimization in gridconnected inverters[J].Proceedings of the CSEE, 2015, 35(2):411-417(in Chinese).

[7]TANG Y, LOH P C, WANG P, et al.Exploring inherent damping characteristic of LCL-filters for three-phase gridconnected voltage source inverters[J].IEEE Transactions on Power Electronics, 2012, 27(3):1433-1443.

[8]邹常跃,陈俊,许树楷,等.长控制链路延时特征下柔性直流输电系统动态性能改善方法[J].电网技术,2017,41(10):3216-3222.

ZOU Changyue, CHEN Jun, XU Shukai, et al.Dynamic performance optimization of VSC-HVDC considering its long delay[J].Power System Technology, 2017, 41(10):3216-3222(in Chinese).

Experimental Investigation on Communication Link Delay of Valve Control System of Ultrahigh-voltage VSC-HVDC

HU Yu1,2*, CHEN Jun3, ZOU Changyue3, ZHOU Jingyu4, LIN Weixing1,2

(1.TBEA China Xinjiang Sunoasis Co., Ltd., Xi'an 710000, Shaanxi Province, China;2.TBEA Xi'an Flexible Power T&D Co., Ltd., Xi'an 710000, Shaanxi Province, China;3.State Key Laboratory of HVDC, Electric Power Research Institute of China Southern Power Grid, Guangzhou 510080, Guangdong Province, China; 4.CSG EHV Power Transmission Company, Guangzhou 510620, Guangdong Province, China)

Abstract: Communication link delay strongly influences the dynamic performance of the modular-multilevel-converterbased high voltage direct current(MMC-HVDC)system.System stability is reduced when link delay is unreasonably designed.The number of single bridge arm submodules has increased owing to the improvement of HVDC systems.This has led to challenges in reducing control and protection delay.In this work, a test method is proposed by analyzing the converter valve control link delay at the Liubei converter station of the Kunliulong HVDC project.The method is utilized to perform tests at the state key laboratory of HVDC, and the optimization method is proposed.The valve control downlink delay, protection link delay and uplink delay is respectively less than 40 μs, 60 μs, and 60 μs.Under the existing hardware level, the valve control link delay has reached the design expectation.

Keywords: modular multilevel converter; converter valve control equipment; time delay

作者简介:

胡煜

胡煜(1982),男,硕士,研究方向为柔性直流输电阀控保护装置相关技术。通信作者,E-mail:huyu2877@sina.com。

陈俊(1986),男,硕士,研究方向为柔性直流输配电技术及电力电子技术。

邹常跃(1989),男,博士,研究方向为柔性直流输电技术及电力电子技术。

周竞宇(1983),男,高级工程师,研究方向为柔性直流输电和高压直流输电技术。

林卫星(1986),男,博士,教授级高级工程师,主要从事直流-直流自耦变压器、直流-直流变换器、直流输电、直流电网、MMC、风力发电等方面的研究。

(责任编辑 张宇)